# DESIGN AND SIMULATION OF MONTGOMERY MULTIPLIER ARCHITECTURE FOR RESIDUE NUMBER SYSTEM(RNS)

Mohamed Uvaise A, Indhuja T, Janarthanan S

<sup>1</sup>Studuent, Dept. of Electronics and Communication Engineering, Bannari Amman Institute of Technology, IN <sup>2</sup>Studuent, Dept. of Electronics and Communication Engineering, Bannari Amman Institute of Technology, IN <sup>3</sup>Studuent, Dept. of Electronics and Communication Engineering, Bannari Amman Institute of Technology, IN

**Abstract** -For effective modular multiplication, the Montgomery multiplier technique is crucial, especially in cryptographic applications such as elliptic curve encryption and RSA. The design and simulation of a Montgomery multiplier architecture specifically adapted for the Arbitrary Residue Number System (RNS) are presented in this work. By removing carry propagation, the RNS improves modular arithmetic and is hence well suited for parallel processing, which speeds up arithmetic processes. The goal of combining RNS and Montgomery multiplication is to improve module multiplication performance, especially for big numbers that are utilized in cryptographic systems. This work's main goal is to provide an efficient Montgomery multiplier architecture that takes advantage of RNS's advantages for high-speed, low-latency operations. An effective structure is used in the suggested design to convert between the standard and the suggested solution makes use of a customized multiplier to carry out Montgomery reduction in the RNS domain and an effective framework for translating between the standard number system and the RNS.

*Key Words:* Montgomery Multiplier, Residue Number System (RNS), ModularMultiplicationCryptography, FPGA, ASIC, Parallel Processing, Hardware Architecture, Throughput

# INTRODUCTION

The integration Modular multiplication is a crucial operation in contemporary cryptography and highperformance computing, serving as the basis for many safe data processing techniques. It is essential to key exchange protocols, encryption, and decryption. when accuracy and computing and efficiency are essential. Montgomery multiplication was presented as an effective technique for modular arithmetic in order to address these issues. This method removes the need for direct division by converting integers into a specific Montgomery representation, greatly increasing computational performance. The design, which is implemented in Verilog, is aimed at highsecurity and resource-constrained contexts, guaranteeing flexibility for a range of cryptography applications. as well as digital signal processing. The project exhibits a scalable solution that satisfies the requirements of contemporary computing through thorough testing and assessment.

The architecture was evaluated for different modulus and residue base sizes, and the simulation results show notable

speedups over conventional modular multiplication methods. Additionally, the suggested design exhibits outstanding scalability, making it appropriate for uses like digital signal processing and encryption methods that demand highthroughput arithmetic. To sum up, this study offers a scalable solution for high-performance modular multiplication by presenting an effective Montgomery multiplier architecture for RNS. . High throughput, space efficiency, and resource usage are important design factors Simulation results show how successful the suggested architecture is in terms of resource utilization and performance

# 1.1 Background of the Work

Montgomery multiplication's main benefit is its capacity to eschew direct division in favor of a sequence of additions and shifts. Montgomery multiplication is therefore especially well-suited for hardware implementations since it significantly reduces computational cost. Montgomery multiplication's effectiveness in modular arithmetic has led to its widespread adoption in cryptographic hardware accelerators, including FPGA and ASIC implementations. The Residue Number System (RNS), an alternate number system for modular arithmetic, has grown in prominence concurrently with developments in Montgomery multiplication. By taking a number modulo a collection of pairwise coprime moduli, RNS breaks it down into a number of smaller parts, or residues. This breakdown makes arithmetic possible. The complexity of carry addition, propagation during subtraction, and multiplication is greatly decreased by allowing operations to be carried out independently on each residue. Which make it perfect for high-speed the main challenges are completing modular reduction following the Montgomery Number. The main advantages of RNS are its ability to enable parallelism and its carry-free nature, both of which make it ideal for high-speed arithmetic operations, especially in hardware conversions effectively while taking advantage of RNS's parallel processing power.

International Research Journal of Education and Technology Peer Reviewed Journal ISSN 2581-7795

#### 1.2 Motivation and Scope of the Proposed Work

Parallel operations made possible by this decomposition can greatly lower latency and increase throughput when executing modular processes. Despite these benefits, Montgomery multiplication integration with RNS is still difficult, mostly because managing modular reductions and number system conversions must be done efficiently. Our goal is to create an architecture that minimizes hardware complexity while increasing modular multiplication speed by leveraging the advantages of both approaches. The following are the main goals of this work: to create a productive multiplier that combines RNS and Montgomery reduction for quicker modular multiplication. to ensure the architecture's viability for hardware implementations such as FPGAs and ASICs by optimizing it in terms of throughput, area, and resource utilization. to evaluate the design's performance in terms of latency, speed, and scalability by simulating it for various modulus sizes and residue bases. to investigate this architecture's potential for high-performance cryptography systems that require quick modular reductions.

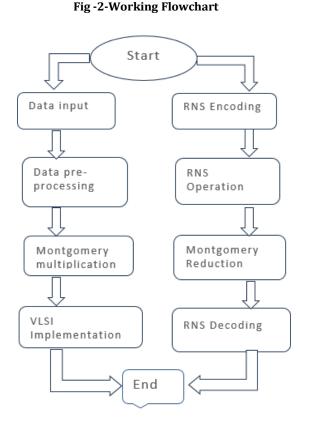

#### 2. METHODOLOGY

This Creating a customized Montgomery multiplier architecture that operates inside the RNS framework is the main task of the methodology. The actions listed below are taken RNS Representation To begin, the RNS displays the input number. This entails breaking down the number into its constituent residues using a collection of pairwise coprime moduli. The system's performance is greatly influenced by the moduli selection. Montgomery Reduction in RNS: Modifying the Montgomery reduction procedure to accommodate RNS is a crucial first step. This calls for the creation of specific algorithms to manage the conversion between the standard number system and RNS, as well as the concurrent execution of modular reduction for every residue. Designing with hardware optimization in mind ensures that the architecture is hardware-friendly and makes effective use of resources such as registers, multipliers, and adders. In order to decrease latency and limit the amount of hardware space needed, the multiplier structure is meticulously adjusted. Lastly, the hardware efficiency (area and resource utilization) and performance (throughput and latency) of the suggested Montgomery multiplier design for RNS are contrasted with those of other modular multiplication methods, such as conventional Montgomery multiplication without RNS. This comparison aids in determining how well the suggested architecture works for application.

#### 2.1 System Architecture

The The Residue Number System (RNS) is used in the system architecture to handle modular multiplications effectively, maximizing speed and power usage. It guarantees the most efficient and least resource-intensive execution of huge modular arithmetic operations, which are common in cryptography and other high-performance applications. A thorough analysis of the system architecture may be found below The System Architecture's Data Flow According to a sequential procedure, input is transformed, calculations are made, and the output is then converted back into binary form in the RNS-based Montgomery Multiplier architecture. The data flow's crucial phases are: Binary inputs are loaded into the architecture to start the system. After passing via the Binary to RNS Converter, these inputs.

#### 2.2 Core Components of the Architecture

The Unit Multiplier One of the main parts of the architecture is the Multiplier Unit, which is in charge of multiplying the transformed inputs a' and b' (obtained by the operation of transform). The multiplier unit takes speed and resource consumption into account when designing it for flexibility and efficiency. The combinational multiplier is an implementation option that prioritizes speed. Because it calculates the output in a single clock cycle without requiring sequential processing, it enables quick multiplication but may consume more resources. Sequential Multiplier: To conserve hardware resources, an alternative is to utilize a sequential multiplier. Although it might sacrifice some speed, this approach allows for a more resource-efficient architecture by carrying out multiplication step-by-step over several clock cycles. Signed and unsigned multiplication are supported by the multiplier unit. The Control Unit oversees all aspects of Montgomery multiplication, including modular reductions, multiplication, and number system conversions. It guarantees synchronization between the various architecture components and organizes the order of operations. Flow Control Each step (conversion, multiplication, and reduction) is carried out according to the control unit's instructions. It initiates the RNS format conversion of inputs, controls the Montgomery multiplier's operation for every residue, and arranges the conversion back to the conventional number system. Timing and Synchronization When working with parallel processing units, the control unit makes sure that everything happens in the right order. outputs from each parallel unit are correctly mixed. In order to ensure that the Montgomery multiplier can function effectively in a variety of real-world scenarios, the goal is to optimize it to reach the necessary speed and performance parameters. The modular reduction is also carried out in parallel following the Montgomery multiplication for every residue.

# International Research Journal of Education and Technology Peer Reviewed Journal ISSN 2581-7795

## Fig -1- Comparison Table for Montgomery Multiplier

| Parameter           | Classical<br>Methods                                            | Proposed<br>Montgomery<br>Multiplier                                               |

|---------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------|

| Area<br>Utilization | Higher resource<br>consumption due<br>to separate<br>multiplier | More resource-<br>efficient with<br>reduced hardware<br>usage.                     |

| Scalability         | Performance<br>degrades with<br>larger operand<br>sizes.        | Effectively handles<br>varying operand<br>sizes with<br>consistent<br>performance. |

| Accuracy            | 100% accuracy,<br>comparable to the<br>proposed design.         | 100% accuracy,<br>reliability for<br>modular arithmetic<br>operations.             |

| Limitation          | Relatively slower<br>with higher<br>computational<br>overhead.  | Significantly faster<br>due to optimized<br>reduction                              |

# 2.3 Increase Computational Effectiveness

The Decomposing big modular multiplications into smaller, concurrent calculations across numerous residue channels is the fundamental concept behind the Montgomery multiplier architecture's use of the Residue Number System (RNS). This enables for significant reduction in the computational load per channel, resulting to faster processing better throughput. Each residue channel handles the modular multiplications independently, boosting the system's overall effectiveness. Because of the effective distribution of the computing load, the architecture is highly parallelized and able to managechallengingmodular arithmetic jobs concurrently. Applications like encryption, where massive modular multiplications must be performed rapidly and frequently, can profit substantially from this.

### 2.4 Boost Performance and Speed

The RNS is perfect for speeding up modular multiplication because it naturally supports parallel processing because each residuechannelfunctionsindependently. Thisparallelismwill befully utilized in the Montgomery multiplier's architecture, leading to a significant speedup over conventional sequential techniques. Faster module multiplication execution times are the main goal of this design, which is especially important for real-time applications like high-throughput cryptographic procedures (like RSA and ECC). In order to ensure that the Montgomery multiplier can function effectively in avariety real-worldscenarios, thegoalis tooptimizeit to reach thenecessary speed and performanceparameters.

#### 2.5 Parallel Processing Units

The Thecapability of RNSto execute activities in parallel isone of its main benefits. This property is exploited by the parallel processing units in this architecture, which carry out several modular multiplications for various residues at once. Multiple residues can be multiplied in parallel modular fashion thanks to the Montgomery multiplier's separate operation on each residue. Since each residue functions in parallel with no carry propagation between them, this greatly accelerates the multiplication operation as a whole. Modular Reduction The modular reduction is also carried out in parallel following the Montgomery multiplication for every residue. High throughput and minimal latency are ensured by each parallel unithand ling the modular reduction for a single residue.

### 2.6 RNS Converter (Number System Conversion Unit)

An essential part of the Montgomery Multiplier Architecture for Arbitrary Residue Number System (RNS) is the RNS Converter. In ordertoeffectivelyperformmodulararithmeticoperations, thisunit is in charge of converting numbers between the normal integer number system and the Residue Number System (RNS).

A number is represented by a set of residues that are obtained by takingthenumbermoduloapredeterminedsetofpairwisecoprime moduliinanon-weightednumbersystemcalled RNS. Becausethese moduli are selected so that they do not share divisors, arithmetic operations can be carried out on each residue independently and concurrently. The RNS converter's primary functions and The outcome must be translated back to the conventional integer number system after the modular multiplication has been completed in the RNS domain. To receive the Montgomery multiplication'sfinaloutputinitsconventionalform, this conversion is required. The Chinese Remainder Theorem (CRT), a mathematical techniquethatreconstructs an integer.

# International Research Journal of Education and Technology Peer Reviewed Journal

Peer Reviewed Journa ISSN 2581-7795

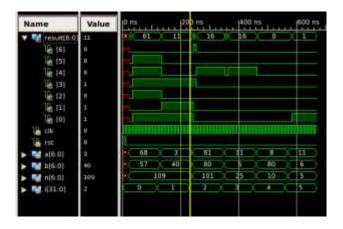

Fig -3-Simulation of Montgomery architecture

# CONCLUSION

This A reliable way to increase the effectiveness of modular arithmetic operations is to develop and simulate the Montgomery Multiplier architecture for an arbitrary Residue Number System (RNS). By avoiding direct division operations, the Montgomery multiplication technique may drastically cut down on computing time, as this work shows. This makes it perfect for applications like error correction, digital signal processing, and cryptography. The architecture increases scalability, minimizes carry propagation, and provides parallelism by utilizing RNS's characteristics. In comparison to conventional modular multiplication techniques, simulation results verify that the suggested architecture offers high-speed and low-power computation while operating at optimal performance for arbitrary RNS bases. In order to verify real-world performance and further optimize, future work might concentrate on putting the idea into practice on hardware platforms like FPGAs or ASICs... High throughput, space efficiency, and resource usage are important design factors Simulation results show how successful the suggested architecture is in terms of resource utilization and performance.

## REFERENCES

- J.-.C. Bajard, L. Imbert, A full RNS implementation of RSA, IEEE Trans. Comput. 53(2004) 769–774.

- [2] J.-.C. Bajard, L. Imbert, A full RNS implementation of RSA, IEEE Trans. Comput. 53(2004) 769–774.

- [3] M. Ciet, M. Neve, E. Peeters, J.-J. Quisquater, Parallel FPGA implementation of RSA with residue number systems-can side-channel threats be avoided?, in: 2003 46th Midwest Symposium on Circuits and Systems, 2003, pp. 806–810.

- [4] .P. Ananda Mohan, Residue number systems: theory and applications, Basel:Birghauser, Math. (2016).

- [5] Z. Wang, G.A. Jullien, W.C. Miller, An algorithm for multiplication modulo (2/spland/n-1), in: Proceedings of the 39th Midwest Symposium on Circuits and Systems,1996, pp. 1301–1304.

- [6] H. Ahmadifar, G. Jaberipur, Improved modulo-(2 n±3) multipliers, in: The 17<sup>th</sup> CSI International Symposium on Computer Architecture & Digital Systems (CADS2013), 2013, pp. 31–35.

@2024, IRJEDT VOLUME - 6 ISSUE - 12 DEC - 2024

673